PowerPC のレジスタ

PowerPCには32本の32bit汎用レジスタ、32本の64bit浮動小数点レジスタ、数本の特殊目的レジスタがあります。スタック専用のレジスタはありません。

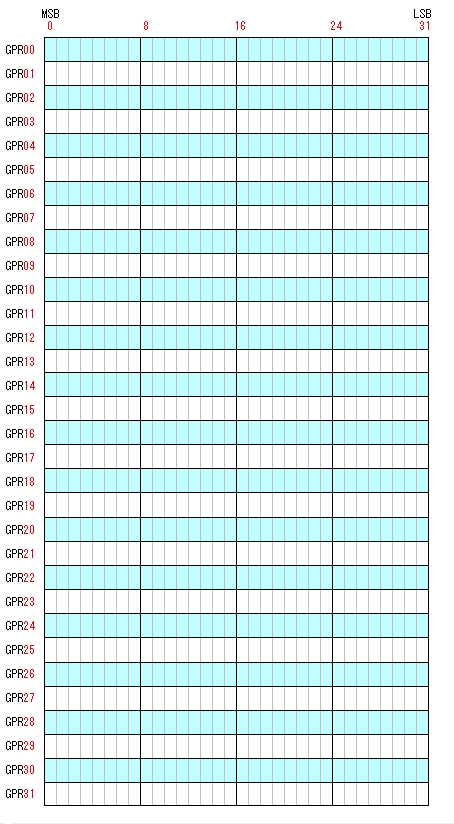

汎用レジスタ

32本の汎用レジスタ(General Purpose Register)があり、演算命令、比較命令、メモリ転送命令など多くの命令のオペランドとして使い、数値、アドレスを格納します。どのレジスタも同じ機能(GPR0だけは一部の命令で特殊な意味がある) を持っています。GNU as (アセンブラ)では、0 から 31の数値でレジスタを指定します。as に「-mregnames」オプションを指定した場合には r0 から r31 と表記することができます。今後、汎用レジスタの表記には r0 - r31 を用います。

ビットの番号付けが他のCPUと逆になっていて、bit0が最上位になります。ローテイト命令などでビット位置を指定する場合に注意が必要です。上位16ビットは0:15、下位16ビットは、16:31となることに注意してください。

PowerPCはスタックポインタを持たないため、汎用レジスタの1つをスタックポインタとして使います。ほとんどのOSと同じく Linux でも r1 をスタックポインタとします。各レジスタはr0を除いてまったく同じ働きをしますが、レジスタの使い方はOSで採用している ABI (Application Binary Interface) で定義された使い方(引数に使用するレジスタ、内容を壊してはいけないレジスタなどの決まり)があります。アセンブリだけでプログラムを作成する場合は、スタックポインタとして使う r1 以外は好きなように使ってかまいません。

32本のレジスタを図にしてみると、かなり多く使えることが分かります。

r0 が 0 と解釈される命令

次の命令で r0 がソースレジスタ(オペランドの2番目のレジスタ)に指定された場合には、 r0の内容ではなく数値 0 として扱われます。

| 演算 | ロード | ストア |

|---|---|---|

| addi | lbz | stb |

| addis | lbzx | stbx |

| lha | ||

| lhax | ||

| lhbrx | sthbrx | |

| lhz | sth | |

| lhzx | sthx | |

| lmw | stmw | |

| lswi | stswi | |

| lswx | stswx | |

| lwbrx | stwbrx | |

| lwz | stw | |

| lwzx | stwx | |

| lwarx | stwcx. |

例えば、次のコードを実行すると r0 の値は「6」になるように思われますが、 r0には「1」が代入されます。

li r0, 0

addi r0, r0, 5

addi r0, r0, 1

addi命令がそれぞれ「r0 = 0 + 5」「r0 = 0 + 1」と解釈されるため、最終的に r0 の値は「1」となります。

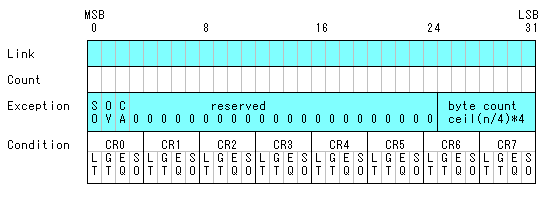

特殊レジスタ

特権モードでは他にも多くの特殊レジスタが使用できますが、ここでは省略します。

リンクレジスタ

リンクレジスタ(Link Register)には、サブルーチン呼び出しに分岐命令を使用した場合に、戻り番地(分岐命令直後のアドレス)が格納されます。

カウントレジスタ

カウントレジスタ(Count Register)は専用の分岐命令と組み合わせてループのカウンタとして使用します。

条件レジスタ

条件レジスタ(Condition Register)は4ビット単位で8組に分かれます。指定しない場合は、CR0(最上位の4ビット)を指定したものとみなされます。演算結果にしたがって条件レジスタ(Condition Register)の対応する各ビットが変化します。

| ビット | フラグ | 意味 |

|---|---|---|

| 0 | 負 (LT) | 結果が負のときにセット |

| 1 | 正 (GT) | 結果が正(かつゼロでない)ときにセット |

| 2 | ゼロ (EQ) | 結果がゼロのときにセット |

| 3 | サマリオーバフロー (SO) | 命令完了時の XER[SO] のコピー |

整数例外レジスタ

整数例外レジスタ(Integer Exception Register)は演算結果のキャリー、オーバーフロー、サマリーオーバーフローの各ビットとstswx (Store String Word Indexed)、 lswx (Load String Word Indexed )の転送バイト数を設定するフィールドを持ちます。

| ビット | フラグ | 意味 |

|---|---|---|

| 0 | SO | 演算でオーバフローが発生したらセット、自動的にリセットされない |

| 1 | OV | 演算でオーバフローが発生したらセット |

| 2 | CA | MSB (最上位ビット) からの桁上り (キャリー) が発生したらセット |

| 25-31 | byte count | stswx/lswxの転送バイト数を設定 |

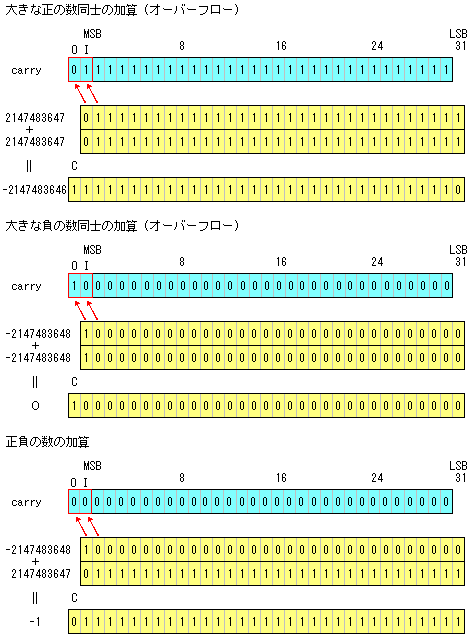

キャリーとオーバーフロー

演算の結果、第0ビット(最上位桁)で桁上り(キャリー)が発生するとキャリーフラグがセットされます。また、2の補数の演算で結果が32ビットに収まらない場合、オーバーフローフラグがセットされます。オーバーフローは大きな正数同士の加算、(絶対値が)大きな負数同士の加算によって発生します。次のように第0ビット(最上位桁)からのキャリーと第1ビットからのキャリーが異なる場合にオーバーフローフラグがセットされます。

乗除算で結果が32ビットに収まらない場合もオーバーフローが発生します。

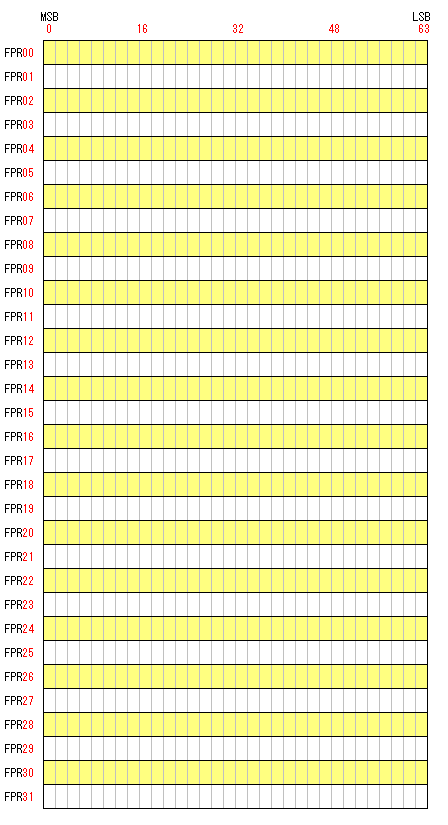

浮動小数点レジスタ

浮動小数点演算専用の64bitレジスタ(Floating Point Register)も32本あります。 IEEE標準の形式で浮動小数点数を格納します。

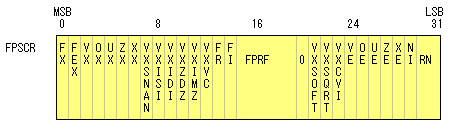

Floating-Point Status and Control Register

浮動小数点演算の状態の保持と制御を行うレジスタです。

詳細は省略します。